Предложен новый тип оперативной памяти, который ускорит развитие искусственного интеллекта

09.02.2021 639 0

Решение задач с использованием искусственного интеллекта сопровождается обработкой огромных массивов данных, которые почти всегда превышают возможности кеш-памяти процессоров. Поэтому для ИИ идеальной будет память внутри процессора и с высокой энергоэффективностью. Такую память предложили отдельно друг от друга исследователи из США и Бельгии.

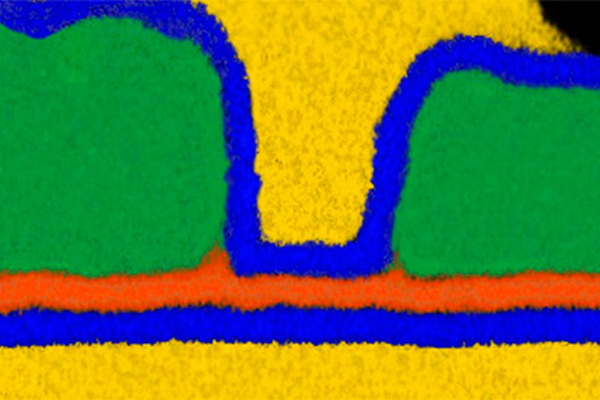

Бесконденсаторная ячейка памяти (оранжевый - легированный вольфрамом оксид индия, жёлтый - затворы транзисторов из палладия, зелёный - электроды стока и истока из никеля, синий - диэлектрик из оксида гафния). Источник изображения: University of Notre Dam.

Как известно, классическая оперативная память DRAM представляет собой схему из одного управляющего транзистора и конденсатора (1T1C), который хранит заряд, тогда в ячейке записана 1 или разряжен, что означает 0. Расход энергии идёт как на запись данных, так и на чтение (при чтении конденсатор теряет часть ёмкости и её надо восполнять), а также на регенерацию данных во всех ячейках с частотой примерно раз в 64 мс. Исследователи из Университета Нотр-Дам в США предложили решить вопрос в корне и представили ячейку DRAM без конденсатора, но с двумя транзисторами - 2T0C.

Идея заключается в том, что затвор транзистора - это маленький конденсатор. Тогда один транзистор в схеме играет роль управляющего транзистора (левый на схеме ниже), а второй хранит заряд (информацию). Кроме того, в предложенной схеме оба транзистора работают независимо, один из которых записывает данные, а второй осуществляет чтение. Например, если в затворе второго транзистора содержится заряд, он открыт и через него течёт ток, который можно «прочесть».

Проблема с реализацией предложенной схемы ровно в одном - не допустить саморазряда в затворе «запоминающего» транзистора. Поэтому исследователи подбирают полупроводниковые материалы, которые минимизируют токи утечки и токи через транзисторы в закрытом состоянии. Обычный кремний для этого не годится. В Университете Нотр-Дам, например, прототип ячейки 2T0C изготовили с использованием оксида индия, легированного до 1 % вольфрамом (IWO). Утверждается, что у получившейся схемы токи утечки на два-три порядка меньше, чем у кремния.

Исследователи из бельгийского центра Imec использовали в схеме 2T0C иные материалы, а именно известную уже по дисплеям Sharp комбинацию IGZO (оксид индия, галлия и цинка). Впрочем, для изготовления памяти 2T0C классические техпроцессы с использованием IGZO не подошли, и пришлось их существенно дорабатывать. Зато память Imec оказалась близкой к энергонезависимой. Среднее время удержания данных в ячейке 2T0C бельгийцев составляло 200 секунд, а 25 % ячеек удерживали заряд свыше 400 секунд, что в тысячи раз дольше, чем в случае обычных ячеек DRAM. Более того, в Imec рассчитывают, что смогут довести время удержания данных в ячейках 2T0C без регенерации до 100 часов и более.

Наконец, ячейки памяти 2T0C, поскольку в них отсутствуют довольно большие по объёму конденсаторы, можно будет изготавливать в рабочих слоях процессоров или над ним. Это означает, что процессор можно будет наделить настолько большим объёмом памяти, что все данные для работы смогут помещаться в памяти в составе процессора. Путь это будет не кеш, но всё равно окажется намного ближе (и быстрее с точки зрения доступа) к логике процессора, чем модули DRAM.

Всё в совокупности сможет поднять выполнение алгоритмов ИИ на новую и недосягаемую сегодня высоту. Обычные компьютеры тоже смогут преобразиться. Осталось только всего этого дождаться.

Бесконденсаторная ячейка памяти (оранжевый - легированный вольфрамом оксид индия, жёлтый - затворы транзисторов из палладия, зелёный - электроды стока и истока из никеля, синий - диэлектрик из оксида гафния). Источник изображения: University of Notre Dam.

Как известно, классическая оперативная память DRAM представляет собой схему из одного управляющего транзистора и конденсатора (1T1C), который хранит заряд, тогда в ячейке записана 1 или разряжен, что означает 0. Расход энергии идёт как на запись данных, так и на чтение (при чтении конденсатор теряет часть ёмкости и её надо восполнять), а также на регенерацию данных во всех ячейках с частотой примерно раз в 64 мс. Исследователи из Университета Нотр-Дам в США предложили решить вопрос в корне и представили ячейку DRAM без конденсатора, но с двумя транзисторами - 2T0C.

Идея заключается в том, что затвор транзистора - это маленький конденсатор. Тогда один транзистор в схеме играет роль управляющего транзистора (левый на схеме ниже), а второй хранит заряд (информацию). Кроме того, в предложенной схеме оба транзистора работают независимо, один из которых записывает данные, а второй осуществляет чтение. Например, если в затворе второго транзистора содержится заряд, он открыт и через него течёт ток, который можно «прочесть».

Проблема с реализацией предложенной схемы ровно в одном - не допустить саморазряда в затворе «запоминающего» транзистора. Поэтому исследователи подбирают полупроводниковые материалы, которые минимизируют токи утечки и токи через транзисторы в закрытом состоянии. Обычный кремний для этого не годится. В Университете Нотр-Дам, например, прототип ячейки 2T0C изготовили с использованием оксида индия, легированного до 1 % вольфрамом (IWO). Утверждается, что у получившейся схемы токи утечки на два-три порядка меньше, чем у кремния.

Исследователи из бельгийского центра Imec использовали в схеме 2T0C иные материалы, а именно известную уже по дисплеям Sharp комбинацию IGZO (оксид индия, галлия и цинка). Впрочем, для изготовления памяти 2T0C классические техпроцессы с использованием IGZO не подошли, и пришлось их существенно дорабатывать. Зато память Imec оказалась близкой к энергонезависимой. Среднее время удержания данных в ячейке 2T0C бельгийцев составляло 200 секунд, а 25 % ячеек удерживали заряд свыше 400 секунд, что в тысячи раз дольше, чем в случае обычных ячеек DRAM. Более того, в Imec рассчитывают, что смогут довести время удержания данных в ячейках 2T0C без регенерации до 100 часов и более.

Наконец, ячейки памяти 2T0C, поскольку в них отсутствуют довольно большие по объёму конденсаторы, можно будет изготавливать в рабочих слоях процессоров или над ним. Это означает, что процессор можно будет наделить настолько большим объёмом памяти, что все данные для работы смогут помещаться в памяти в составе процессора. Путь это будет не кеш, но всё равно окажется намного ближе (и быстрее с точки зрения доступа) к логике процессора, чем модули DRAM.

Всё в совокупности сможет поднять выполнение алгоритмов ИИ на новую и недосягаемую сегодня высоту. Обычные компьютеры тоже смогут преобразиться. Осталось только всего этого дождаться.

| Читайте также |

| Комментарии (0) |